# 1. Scope

This specification covers the Electrical Viewfinder with a full color Ferroelectric Liquid Crystal (FLC) display module to be delivered from SONICOM.

## 2. Specification summary

#### **Table1: Specification summary**

| Parameter                 | Specifications                                        |

|---------------------------|-------------------------------------------------------|

| Display Technology        | Ferroelectric Liquid Crystal (FLC) on reflective CMOS |

| Display Mode              | Field sequential color                                |

| Display Format            | 720(H) x 540(V) *2                                    |

| Display Panel Active Area | 3.96 x 2.97mm *2                                      |

| Display Area diagonal     | 4.95mm (0.195") *2                                    |

| Input Grayscale           | 256 levels                                            |

| Color Depth               | 4.2Million unique colors (YCrCb video interface)      |

| Pixel Fill Factor         | 88%                                                   |

| Display Pixel Pitch       | 5.5um                                                 |

| Display Frame Rate        | 60 Hz/360Hz (NTSC), 50Hz/300 Hz (PAL)                 |

| Data Clock Rate           | 36 MHz (Typical)                                      |

| Maximum Brightness        | 200 cd/m <sup>2</sup> or more                         |

| Contrast Ratio            | 150:1(Typical)                                        |

| White Point               | (x, y)=(0.313, 0.329) Typical                         |

| Digital Display Interface | YCbCr(4:2:2)-parallel (16 data, Hd, Vd, Clock)        |

|                           |                                                       |

| Control Interface         | Industry-standard two-wire bidirectional serial       |

| Operating Supply Voltages | 1.8 V (Core)                                          |

|                           | 3.3 V (Analog, I/O)                                   |

|                           | 3.3 V (Analog, LED)                                   |

|                           | VIO_serial (Serial interface I/O)                     |

| Iput Signal Level         | CMOS 1.8V~3.3V                                        |

| Power consumption *1      | 180mW(Reference)                                      |

| Size (L×W×H)              | 20.6 x 17.8 x 13.3 (mm)                               |

| Weight                    | TBD                                                   |

| Operating Temperature     | -10°C ~ 70°C (at Surface of Panel)                    |

| Storage Temperature       | -30°C ~ 83°C                                          |

\*1 Typical value at 60 Hz NTSC (gamma correction of 2.1),

Operation with flat field video pattern(data=FFh) at room temperature under the following values. VCC=1.80V, VCCX=3.00V, DAVCC=3.30V, VIO\_serial=3.30V

\*2 The above sizes of the display format, display panel active area and display area diagonal shows the muximum display size available.

Real VGA(640 x 480) display or other lower resolution setting is also available. According to the lower display area, a custom aperture is also available.

# 3.Product Appearance

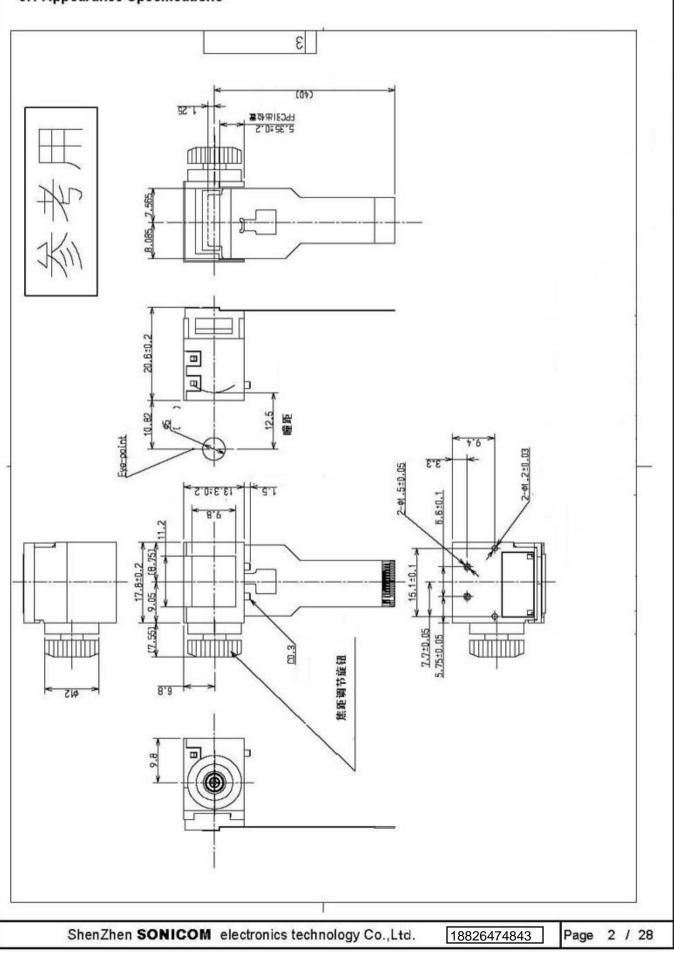

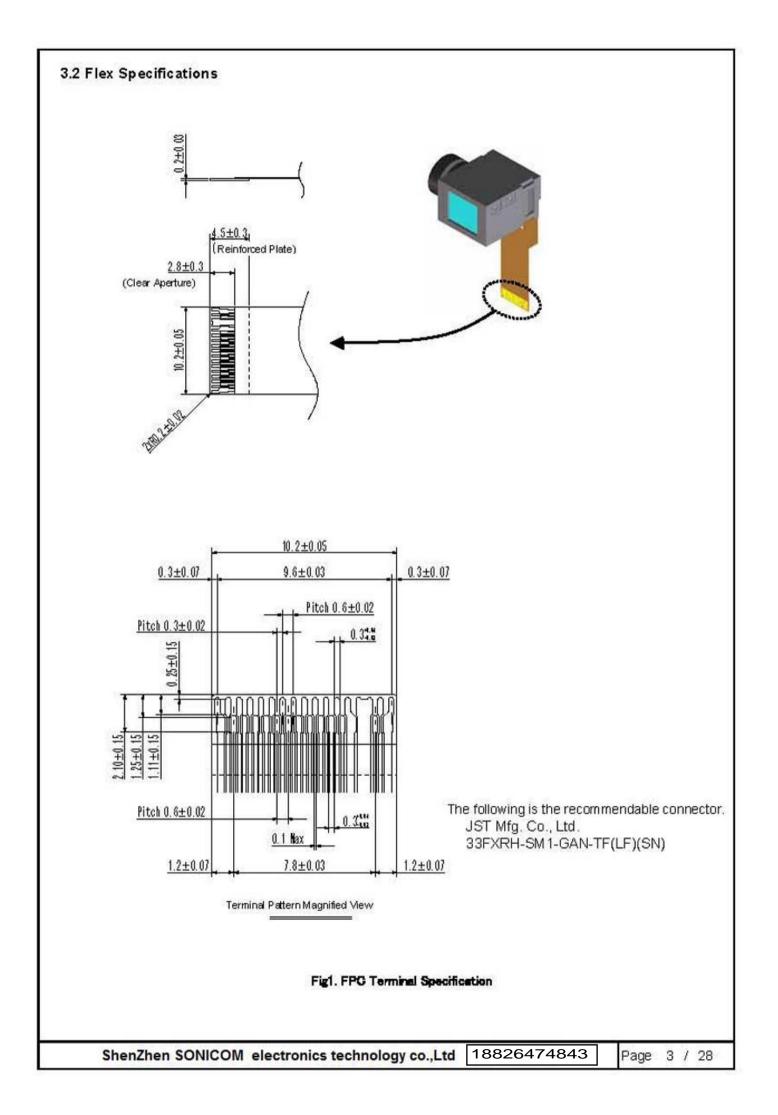

# 3.1 Appearance Specifications

### 4. Electrical Characteristics

#### 4.1 Degital Video Interface

#### 4.1-1 Video Input Signal Format

The following two kinds of input formats are applicable to this product.

1) YCbCr 4:2:2 Format 16bit Parallel

2) YCbCr 4:2:2 Format 8bit Serial

#### 4.1-2 Video Input Signal Timing

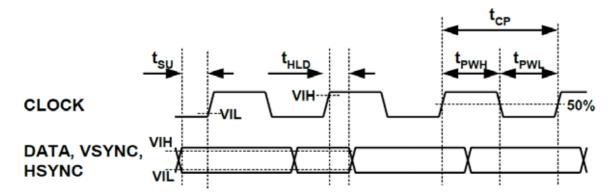

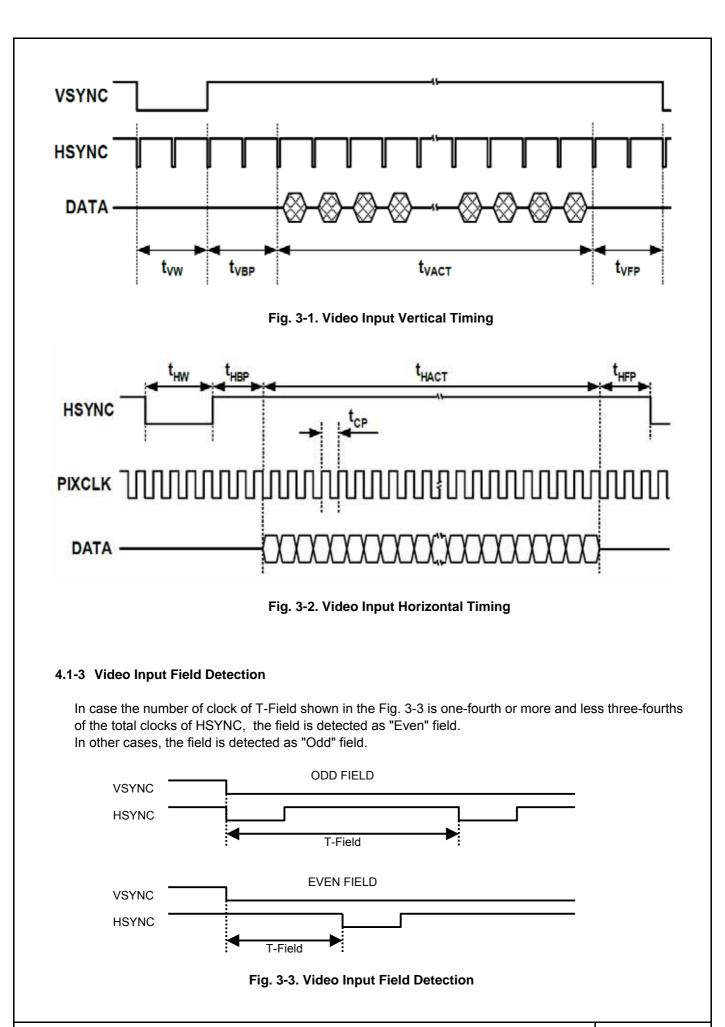

All video input signals must meet the timing requirements shown in the Fig. 2, 3-1, 3-2 & Table 3, 4-1, 4-2, 4-3.

Fig. 2. Video Input Signal Timing

| Parameter                       | Simbol            | Min.                | Тур.                | Max.                | Unit |

|---------------------------------|-------------------|---------------------|---------------------|---------------------|------|

| CLOCK, rate                     | 1/t <sub>CP</sub> | 25                  | 36                  | 75                  | MHz  |

| CLOCK, pulse width high         | t <sub>PWH</sub>  | 40% t <sub>CP</sub> | 50% t <sub>CP</sub> | 60% t <sub>CP</sub> | NA   |

| CLOCK, pulse width low          | t <sub>PWL</sub>  | 40% t <sub>CP</sub> | 50% t <sub>CP</sub> | 60% t <sub>CP</sub> | NA   |

| DATA、VSYNC、HSYNC、<br>setup time | t <sub>su</sub>   | 1.25                |                     |                     | ns   |

| DATA、VSYNC、HSYNC、<br>hold time  | t <sub>HLD</sub>  | 1.25                |                     |                     | ns   |

ShenZhen **SONICOM** electronics technology Co.,Ltd.

Page 5 / 28

| Parameter                 | Symbol                                                                       | Min.   | Тур. | Max. | Unit   |

|---------------------------|------------------------------------------------------------------------------|--------|------|------|--------|

| VSYNC, frequency          | t <sub>vF</sub>                                                              | 47     |      | 63   | Hz     |

| VSYNC, total lines        | t <sub>vtot</sub> =<br>t <sub>vblk</sub> + t <sub>vact</sub>                 | 282    |      | 1088 | Lines  |

| VSYNC, active lines       | t <sub>VACT</sub>                                                            |        | 480  |      | Lines  |

| VSYNC, blanking           | t <sub>VBLK</sub> =<br>t <sub>VFP</sub> + t <sub>VW</sub> + t <sub>VBP</sub> | 12     |      | 200  | Lines  |

| VSYNC, front porch (*1)   | t <sub>VFP</sub>                                                             | 5 (*1) |      | 94   | Lines  |

| VSYNC, pulse width        | t <sub>vw</sub>                                                              | 3      |      | 94   | Lines  |

| VSYNC, back porch         | t <sub>VBP</sub>                                                             | 3      |      | 94   | Lines  |

| HSYNC, total clocks       | t <sub>HTOT</sub> =<br>t <sub>HBLK</sub> + t <sub>HACT</sub>                 | 524    |      | 1392 | Clocks |

| HSYNC, active clocks (*2) | t <sub>HACT</sub>                                                            |        | 640  |      | Clocks |

| HSYNC, blanking           | t <sub>HBLK</sub> =<br>t <sub>HFP</sub> + t <sub>HW</sub> + t <sub>HBP</sub> | 24     |      | 512  | Clocks |

| HSYNC, front porch        | t <sub>HFP</sub>                                                             | 12     |      | 512  | Clocks |

| HSYNC, pulse width        | t <sub>HW</sub>                                                              | 4      | 1    | 128  | Clocks |

| HSYNC, back porch         | t <sub>HBP</sub>                                                             | 8      |      | 512  | Clocks |

| CLOCK, rate               | 1/t <sub>CP</sub>                                                            | 25     |      | 75   | MHz    |

#### Table 4-1. Parallel Data AC Characteristcs Video Format Timing

\*1: The minimum VSYNC front porch must be greater than 5,000 clocks.\*2: Defalt setting is applicable to VGA(640H X 480V) active data input only. When other active date input is needed, please contact us.

| Parameter               | Simbol                                                                       | Min.   | Тур. | Max. | Unit   |

|-------------------------|------------------------------------------------------------------------------|--------|------|------|--------|

| VSYNC, frequency        | t <sub>VF</sub>                                                              | 47     |      | 63   | Hz     |

| VSYNC, total lines      | t <sub>vtot</sub> =<br>t <sub>vblk</sub> + t <sub>vact</sub>                 | 492    |      | 1088 | Lines  |

| VSYNC, active lines     | t <sub>vact</sub>                                                            |        | 480  |      | Lines  |

| VSYNC, blanking         | t <sub>VBLK</sub> =<br>t <sub>VFP</sub> + t <sub>VW</sub> + t <sub>VBP</sub> | 12     |      | 200  | Lines  |

| VSYNC, front porch (*1) | t <sub>VFP</sub>                                                             | 5 (*1) |      | 94   | Lines  |

| VSYNC, pulse width      | t <sub>vw</sub>                                                              | 3      |      | 94   | Lines  |

| VSYNC, back porch       | t <sub>VBP</sub>                                                             | 3      |      | 94   | Lines  |

| HSYNC, total clocks     | t <sub>HTOT</sub> =<br>t <sub>HBLK</sub> + t <sub>HACT</sub>                 | 1316   |      | 3286 | Clocks |

| HSYNC, active clocks    | t <sub>HACT</sub>                                                            |        | 1280 |      | Clocks |

| HSYNC, blanking         | t <sub>HBLK</sub> =<br>t <sub>HFP</sub> + t <sub>HW</sub> + t <sub>HBP</sub> | 36     |      | 512  | Clocks |

| HSYNC, front porch      | t <sub>HFP</sub>                                                             | 24     |      | 512  | Clocks |

| HSYNC, pulse width      | t <sub>HW</sub>                                                              | 4      |      | 128  | Clocks |

| HSYNC, back porch       | t <sub>HBP</sub>                                                             | 8      |      | 512  | Clocks |

| CLOCK, rate             | 1/t <sub>CP</sub>                                                            | 50     |      | 76   | MHz    |

Table 4-2. Serial Data AC Characteristcs Video Format Timing

\*1: The minimum VSYNC front porch must be greater than 5,000 clocks.

\*2: Defalt setting is applicable to VGA(640H X 480V) active data input only. When other active date input is needed, please contact us.

## **4.2 Control Interface**

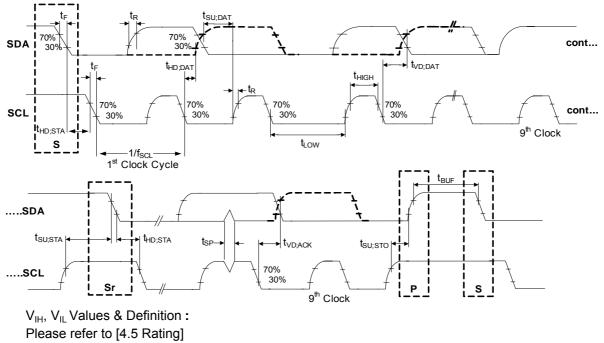

## 4.2-1 AC Characteristics of Interface Signal

This product is controlled by writing data in the control registers with I2C interface. The AC characteristics of interface signal are as follows.

Fig. 5. I2C Interface Signal

| Symbol  | Parameter                                                               | Conditions                                                   |      | d-Mode | Fast-Mod | е    | Unit |

|---------|-------------------------------------------------------------------------|--------------------------------------------------------------|------|--------|----------|------|------|

|         |                                                                         |                                                              | Min. | Max.   | Min.     | Max. |      |

| fSCL    | SCL clock frequency                                                     |                                                              | 0    | 100    | 0        | 400  | KHz  |

| tHD;STA | hold time (& repeated)<br>START condition                               | After this period,<br>the first clock pulse<br>is generated. | 4    | -      | 0.6      | -    | us   |

| tLOW    | LOW period of the SCL clock                                             |                                                              | 4.7  | -      | 1.3      | -    | us   |

| tHIGH   | HIGH period of the SCL clock                                            |                                                              | 4    | -      | 0.6      | -    | us   |

| tSU;STA | set-up time for a repeated<br>START condition                           |                                                              | 4.7  | -      | 0.6      | -    | us   |

| tHD;DAT | data hold time                                                          |                                                              | 0    | -      | 0        | -    | us   |

| tSU;DAT | data set-up time                                                        |                                                              | 250  | -      | 100      | -    | ns   |

| tr      | rise time of both SDA and<br>SCL signals                                |                                                              | -    | 1000   | 20+0.1Cb | 300  | ns   |

| tf      | fall time of both SDA and SCL signals                                   |                                                              | -    | 300    | 20+0.1Cb | 300  | ns   |

| tSU;STO | set-up time for STOP condition                                          |                                                              | 4    | -      | 0.6      | -    | us   |

| tBUF    | bus free time between<br>STOP and START<br>condition                    |                                                              | 4.7  | -      | 1.3      | -    | us   |

| Cb      | capacitive load for each<br>bus line (depends on<br>load and frequency) |                                                              | -    | 400    | -        | 400  | pF   |

| tVD;DAT | data valid time                                                         |                                                              | -    | 3.45   | -        | 0.9  | us   |

## Table 5. AC Characteristics (I2C Interface)

## 4.2-2 Protcol

This FLC device is always considered a slave in the system and requires a clock to be provided to it for all I2C interface transactions.

Start Condition : A start condition is generated through the use of pulling down the SDA line while SCL is still high.

Slave Address : 7bit -- 0111110b

R/!W bit : The 8th bit -- If a READ is requested then the bit should be kept high, and if a WRITE is requested, the line is pulled down to a low-level signal.

- ACK bit : The 9th bit -- the acknowledgment bit from the addressed device. If the addressed device receives its address and is not busy at that time it will respond by pulling the SDA line low and therefore signaling an acknowledgment. If an acknowledgment is detected by the issuing device, then the rest of the message can be sent.

- Stop Condition : If SCL is kept high and SDA changes from low to high, the interface stops.

### Single Write Protocol

A START signal must be presented first. This is when the SDA line is pulled low while the SCL line is kept high. The first byte sent is always the slave address for the qHD panel's I2C interface (0111 110b) followed by the R/!W bit(Lo). An acknowledge (ACK) is returned from the receiving device after each byte sent by pulling the SDA line low for one clock. The clock is still provided by the master device, which is never the qHD panel display. The second byte sent in the write transactions is the qHD panel's 8-bit register address that will be written. After the register address is sent, the byte to be written.

| S | Slave address | R/!W | ACK | Regi address | ACK | Data | ACK | Р |  |

|---|---------------|------|-----|--------------|-----|------|-----|---|--|

|   | SA6SA0        | Lo   |     | RA7RA0       |     | D7D0 |     |   |  |

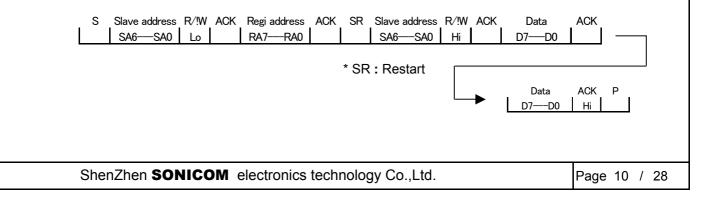

## **Single Read Protocol**

After a START, the slave address and R/!W(Lo) are sent. After an ACK is returned from the receiving device, the register address to be read is sent. Again after an ACK is returned from the receiving device, a START signal is presented again and the slave address is sent followed by the R/!W bit(Hi). After an ACK is returned, the device reads the byte data but not return an ACK. Then, the SDA line is changed from Lo to Hi with keeping the SLC Hi and the interfacing is over.

| S | Slave address | R/!W | ACK | Regiaddress | ACK | SR | Slave address | R⁄!W | ACK | Data | ACK | Р | _ |

|---|---------------|------|-----|-------------|-----|----|---------------|------|-----|------|-----|---|---|

|   | SA6SA0        | Lo   |     | RA7RA0      |     |    | SA6SA0        | Hi   |     | D7D0 | Hi  |   |   |

\* SR : Restart

## **Multi-Write Protocol**

Similar to single write protocol, after transactions of a START, the slave address, R/W!(Lo), an ACK, and byte data in that order, by continuously outputting data, the register address is auto-incremented for each byte write. After all data are written in the necessary addresses, the SDA line is changed from Lo to Hi with keeping the SLC Hi and the interfacing is over.

| S | Slave address | R∕!W | ACK | Regi address | ACK | Data | ACK | Data | ACK | Р | _ |

|---|---------------|------|-----|--------------|-----|------|-----|------|-----|---|---|

|   | SA6SA0        | Lo   |     | RA7RA0       |     | D7D0 |     | D7D0 |     |   |   |

#### **Multi-Read Protocol**

Similar to single read protocol, after transactions of a START, the slave address, R/W!(Lo), an ACK, the register address, a START(SR), the slave address, R/!W(Hi) and an ACK in that order, by continuously reading data, the register address in the device is auto-incremented and the data is output. After all data are read in the necessary addresses, not returning an ACK, the SDA line is changed from Lo to Hi with keeping the SLC Hi and the interfacing is over.

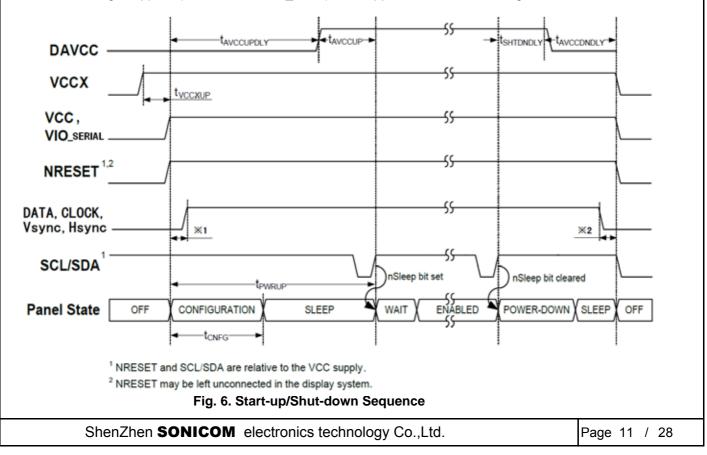

#### **4.3 Control Sequence Requirements**

Timing/sequence requirements must be met during start-up and shut-down of the display panel to avoid damages to the display panel.

#### 4.3-1 Start-up Sequence Requirements

The VCCX power supply must be present before the VCC power suppy is present. After the VCCX power supply is present, the VCC, VIO\_serial must be present for a time period of tVCCXUP. After the voltage supplies (VCC, VIO\_serial) are present and in specification, the NRESET input is high and the CLOCK input is toggling, the display panel will load default register values from non-volatile memory to RAM for a time period of tCNFG. During this time period, the two-wire serial interface is ignored. Although the voltage supplies (VCC, VCCX, VIO\_serial) can be present simultaneously, the tCNFG starts when the VCC power supply is in specification and the NRESET input is high.

(\* As the NRESET is pulled up, the NRESET becomes high even on an open state when the VCC power supply is present.)

After the tCNFG period, the display panel will be in the Sleep mode and the two-wire serial interface is active. After a time period of tPWRUP( The tPWRUP starts when the VCC power supply is in specification and the NRESET is high.), the nSleep bit can be cleared by using the serial interface.

The voltage supplies (VCC, VCCX, VIO\_serial) must be present for a time period of tAVCCUPDLY before the DAVCC power supply is present. A minimum time period of tAVCCUP exists which is time from when the DAVCC supply is present till when the nSleep bit can be cleared. If a valid video signal is not present or the nSleep bit is not cleared, the display panel keeps the Sleep mode and no image is driven. The video signal (DATA0~15,CLOCK,Vsync,Hsync) must be present at the time when or after all the voltage supplies (VCC,VCCX,VIO\_serial) are present as shown in Figure 6. When a video signal is detected and the nSleep bit is cleared, a voltage is supplied to the liquid crystal in the display and images are driven.

## 4.3-2 Shut-down Sequence

In case of shut-down of the display, an operationg voltage to the liquid crystal must be shut by putting the display panel into sleep mode before the voltage supplies are stopped.

After nSleep bit is set through the serial interface, each power supply including the DAVCC and the NRESET must be kept high for a time period of tSHTDNDLY. After that, the DAVCC power supply is stopped first and, after a time period of tAVCCDNDLY, the voltage supplies (VCC, VCCX, VIO\_serial) must be stopped. However, the video signals(DATA0~15,CLOCK,Vsync,Hsync)must be stopped before the voltage supplies (VCC, VCCX, VIO\_serial) are stopped as shown %2 in Figure 6.

| Parameter                                                                                              | Symbol                 | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------------------------------------------------------|------------------------|------|------|------|------|

| Time from VCCX supply to VCC,VIO_serial supply                                                         | t <sub>vccxup</sub>    | 0    | -    | 5    | ms   |

| Time from VCC supply and NRESET Hi till when Configuration is finished.                                | t <sub>CNFG</sub>      | 23   | -    | 40   | ms   |

| Time from VCC supply and<br>NRESET Hi till when nSleep bit can<br>be cleared through serial interface. | t <sub>PWRUP</sub>     | 40   | -    | -    | ms   |

| Time from VCCX,VCC,VIO_serial<br>supply till when DAVCC can be<br>supplied.                            | t <sub>avccupdly</sub> | 400  | -    | -    | us   |

| Time from DAVCC supply till when<br>nSleep bit can be cleared through<br>serial interface.             | t <sub>avccup</sub>    | 1    | -    | -    | ms   |

| Time from when nSleep bit is set<br>through serial interface till when<br>DAVCC supply can be stopped. | t <sub>shtdndly</sub>  | 1    | -    | -    | ms   |

| Time from when DAVCC supply is<br>stopped till when<br>VCCX,VCC,VIO_serial supplies can be<br>stopped. | t <sub>avccdndly</sub> | 40   | -    | -    | ms   |

#### 4.3-3 Sleep Mode

During a Sleep mode, the diplay holds each register value, and when a Sleep mode is cleared, the display becomes an ordinal operation mode. During a Slep mode, the serial interface is available and reading & writing are available without any input of clock.

#### 4.3-4 Complementary Precaution Statements

\* When each register is written with a certain value, the value reflects the operation of the display.

- \* To prevent the display image from being distorted or other failure, the nSleep bit must be cleared while a video signal (DATA0~15,CLOCK,Vsync,Hsync) is present.

- \* if the nSleep bit is cleared during a period other than the time from the Vsync to {the value set in the vvld\_delay register(0Ch) 2}line, the vertical position of the image primarily displayed may be shifted from the proper position.

## 4.4 Pin Assignments

## Table 7. Pin Assignments

| No       | Name       | I/O | Power Supply | Function                 |                       |

|----------|------------|-----|--------------|--------------------------|-----------------------|

|          |            |     |              | 16bit Parallel           | 8bit Serial           |

| 1,2      | GND        | NA  | NA           | Ground                   |                       |

| 3        | DATA 15    | I   | 1.8V ~ 3.3V  | Cb7/Cr7                  | GND                   |

| 4        | DATA 14    | I   | 1.8V ~ 3.3V  | Cb6/Cr6                  | GND                   |

| 5        | DATA 13    | 1   | 1.8V ~ 3.3V  | Cb5/Cr5                  | GND                   |

| 6        | DATA 12    | I   | 1.8V ~ 3.3V  | Cb4/Cr4                  | GND                   |

| 7        | DATA 11    | I   | 1.8V ~ 3.3V  | Cb3/Cr3                  | GND                   |

| 8        | DATA 10    | 1   | 1.8V ~ 3.3V  | Cb2/Cr2                  | GND                   |

| 9        | DATA 9     |     | 1.8V ~ 3.3V  | Cb1/Cr1                  | GND                   |

| 10       | DATA 8     | I   | 1.8V ~ 3.3V  | Cb0/Cr0                  | GND                   |

| 11       | DATA 7     | I   | 1.8V ~ 3.3V  | Y7                       | Y7/Cb7/Cr7            |

| 12       | DATA 6     | I   | 1.8V ~ 3.3V  | Y6                       | Y6/Cb6/Cr6            |

| 13       | DATA 5     |     | 1.8V ~ 3.3V  | Y5                       | Y5/Cb5/Cr5            |

| 14       | DATA 4     | I   | 1.8V ~ 3.3V  | Y4                       | Y4/Cb4/Cr4            |

| 15       | DATA 3     | I   | 1.8V ~ 3.3V  | Y3                       | Y3/Cb3/Cr3            |

| 16       | DATA 2     | I   | 1.8V ~ 3.3V  | Y2                       | Y2/Cb2/Cr2            |

| 17       | DATA 1     |     | 1.8V ~ 3.3V  | Y1                       | Y1/Cb1/Cr1            |

| 18       | DATA 0     | I   | 1.8V ~ 3.3V  | Y0                       | Y0/Cb0/Cr0            |

| 19       | HSYNC      | I   | 1.8V ~ 3.3V  | Horizontal Synch Sign    | al                    |

| 20       | GND        | NA  | NA           | Ground                   |                       |

| 21       | VYSNC      | 1   | 1.8V ~ 3.3V  | Vertical Synch Signal    |                       |

| 22       | VIO_Serial | NA  | NA           | I/O voltage supply for   | serial interface pins |

| 23       | SCL        | I   | VIO_Serial   | Serial Interface Clock   | Input                 |

| 24       | SDA        | 10  | VIO_Serial   | Serial Interface Data I/ | 0                     |

| 25,26    | DAVCC      | NA  | NA           | LED Driver Power Sup     | oply (+3.3V)          |

| 27,28,29 | VCC(*3)    | NA  | NA           | Panel Core Power Sup     | oply (+1.8V)          |

| 30       | VCCX       | NA  | NA           | Panel / EEPROM Pow       | ver Supply (+3.3V)    |

| 31       | CLOCK      | I   |              | Video Data Clock         |                       |

| 32,33    | GND        | NA  | NA           | Ground                   |                       |

\*1: A mapping of video data signal for DATA0~15 can be changed. The details are referred to in [5.Configuration Register Settings].

\*2: It is recommendable to put a 10uF or larger decoupling capacitor to the VCC on a operation circuit side.

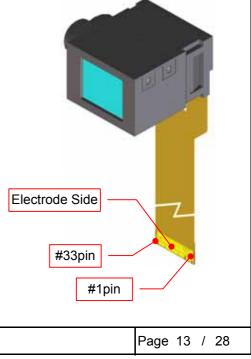

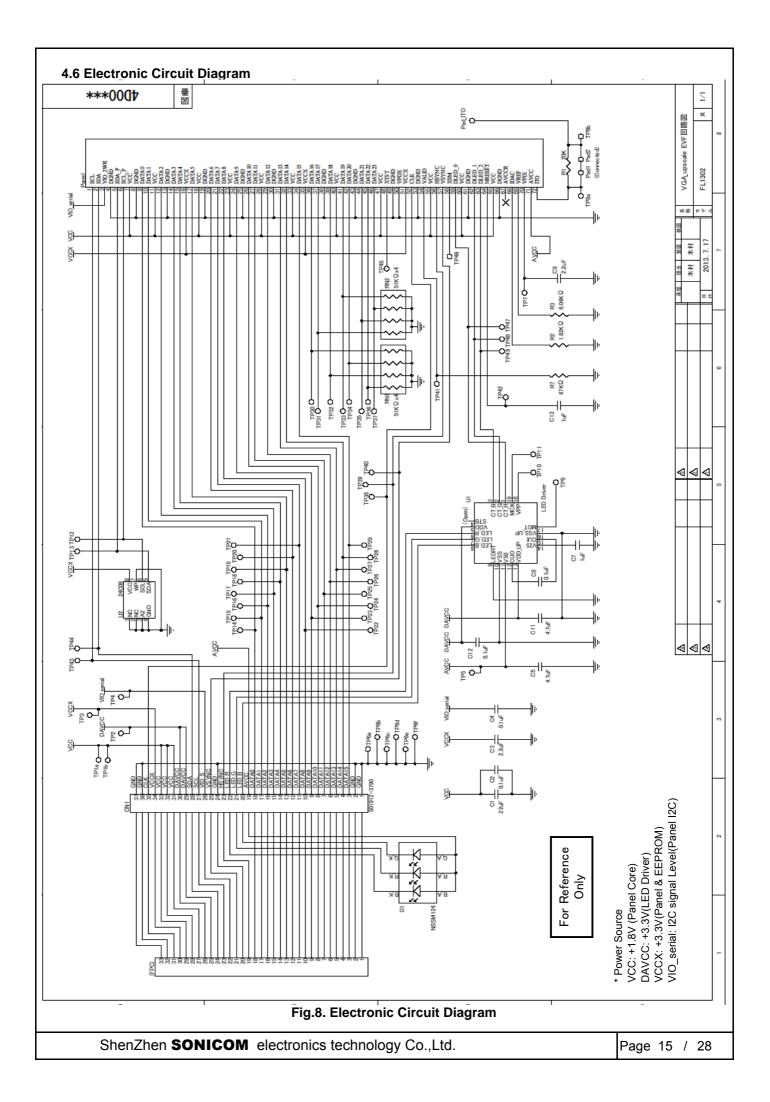

Fig. 7. Pin Location

ShenZhen **SONICOM** electronics technology Co.,Ltd.

# 4.5 Ratings

## Table 8. Absolute Maximum Ratings

| Parameter                       | Absolute Ma | aximum Rating  | Unit |

|---------------------------------|-------------|----------------|------|

|                                 | Min.        | Max.           |      |

| VCCX                            | -0.5        | 3.6            | V    |

| VCC                             | -0.5        | 1.95           | V    |

| DAVCC                           | -0.5        | 3.6            | V    |

| V <sub>IO_Serial</sub>          | -0.5        | 3.6            | V    |

| Voltage on any Video Input Pin  | -0.4        | VCCX + 0.4     | V    |

| Voltage on any Serial Input Pin | -0.4        | VIO_Serial+0.4 | V    |

# Table 9. DC Characteristics

| Parameter                                        | Symbol             | Condition                                     | Rating              |       |                     |    |

|--------------------------------------------------|--------------------|-----------------------------------------------|---------------------|-------|---------------------|----|

|                                                  |                    |                                               | Min.                | Тур.  | Max.                |    |

| Power Supply Voltage                             | VCCX               | *1                                            | 2.9                 | 3.0   | 3.1                 | V  |

|                                                  | VCC                | *1                                            | 1.8                 | 1.8   | 1.95                |    |

|                                                  | DAVCC              | *1                                            | 3.0                 | 3.3   | 3.6                 |    |

|                                                  | VIO_serial         | *1                                            | 1.65                | 3.3   | 3.6                 |    |

| *1: While operating, th                          | ne VCCX and        | VCC must fulfill the at                       | ove condit          | ions. |                     |    |

| nput Voltage                                     | VIH                | For all video inputs<br>For all serial inputs | 0.8*VCC<br>0.8*VIO_ |       |                     | V  |

|                                                  | VIL                | For all video inputs<br>For all serial inputs |                     |       | 0.18*VC<br>0.18*VIO |    |

| nput Capacitance                                 | IC                 | For all inputs<br>3.3Vp-p, f=5MHz             |                     | 6     | 12                  | pF |

| Input Leakage Current                            | IIL                | VI = VIL                                      | -10                 |       |                     | uA |

|                                                  | ШН                 | VI = VIH                                      |                     |       | 10                  |    |

| verage panel operating upply current             | Ivccx              | Nomal Mode                                    |                     | 4.8   | 6                   | mA |

| <pre>Measurement Conditions&gt; /CC=1.80V,</pre> |                    | Sleep Mode                                    |                     | 2.1   | 3                   |    |

| /CCX=3.30V,<br>DAVCC=3.30V,                      | Ivcc               | Nomal Mode                                    |                     | 80    | 86                  |    |

| /IO_serial=3.30V,<br>nput Resolution=640x480     |                    | Sleep Mode                                    |                     | 1.8   | 5                   |    |

| 16bit parallel),<br>Display Resolution=720*54    | I <sub>DAVCC</sub> | Nomal Mode                                    |                     | 6     | 12                  |    |

| Scaling Up),<br>mage = White Raster              |                    | Sleep Mode                                    |                     | 3     | 5                   |    |

| CLOCK =40MHz,<br>Field Frequency=60Hz            | IVIO_serial        | Normal Mode                                   |                     | 0.1   | 0.5                 |    |

| ,                                                |                    | Sleep Mode                                    |                     | 0.1   | 0.5                 |    |

ShenZhen **SONICOM** electronics technology Co.,Ltd.

Page 14 / 28

## 5. Configuration Register Settings

#### **Register Index : 00h**

| Bit         | 7                | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

|-------------|------------------|---|---|-----|------|---|---|---|

| Meaning     | dither_mode[3:0] |   |   | Res |      |   |   |   |

| Value(e.g.) | 0000             |   |   |     | 0000 |   |   |   |

Dither\_Mode: Select dither mode

4'h1=1/2bit Spatial Dither , 1/4bit Temporal Dither

4'h2=1/2bit Temporal Dither, 1/4bit Spatial Dither

4'h3=1/2bit Spatial Dither

4'h5=Reserved (Not Available)

4'h6=Reserved(Not Available)

other= No Dither / Input data rounded to 7-bit values

Res: Reserved

The data of all "Res" register must be 0h for the proper operation.

## Register Index : 01h

| Bit         | 7              | 6                | 5 | 4                 | 3  | 2             | 1  | 0 |

|-------------|----------------|------------------|---|-------------------|----|---------------|----|---|

| Meaning     | cspace_<br>sel | channel_map[2:0] |   | data_channel[1:0] |    | data_seq[1:0] |    |   |

| Value(e.g.) | 1              | 000              |   |                   | 01 |               | 00 |   |

cspace\_sel: Color Space Select

the data must be "1" for this display panel.

channel\_map: select mapping of data channel to color information, dependent on the data channel setting according to the following table.

| channel_map | 16-bit YCbCr             |       | 8-bit YCbCr |         |  |

|-------------|--------------------------|-------|-------------|---------|--|

|             | [15:8]                   | [7:0] | [15:8]      | [7:0]   |  |

| 0h          | Cb/Cr                    | Y     |             | Y/Cb/Cr |  |

| 1h          | Y Cb/Cr Y/Cb/Cr          |       |             |         |  |

| 2h~7h       | Reserved (Not Available) |       |             |         |  |

data\_channel: select data interface

01=16bit data interface

10=8bit data interface

other=Reserved(Not Available)

data\_seq: data sequence of color information for 8-bit and 16-bit interfaces.

| DataSequence | 16-bit YCbCr             | 8-bit YCbCr                                |

|--------------|--------------------------|--------------------------------------------|

| 00           | Reserved (Not Available) | [Cb][Y <sub>0</sub> ][Cr][Y <sub>1</sub> ] |

| 01           | [Y₀Cr] [Y₁Cb]            | [Cr][Y₀][Cb][Y₁]                           |

| 10           | Reserved (Not Available) | [Y <sub>0</sub> ][Cb][Y <sub>1</sub> ][Cr] |

| 11           | Reserved (Not available) | [Y <sub>0</sub> ][Cr][Y <sub>1</sub> ][Cb] |

# 6.Display Panel Specification

# 6.1 Optical Characteristics

## Table 10. Optical Characteristics (at Room Temp.)

| Item            | Conditions                      | Min. | Тур.  | Max.  | Unit  |                   |

|-----------------|---------------------------------|------|-------|-------|-------|-------------------|

| Brightness      | White Raster Image              |      | 200   | 220   |       | cd/m <sup>2</sup> |

|                 | Measure the brightness of       |      |       |       |       |                   |

|                 | the center of the display.      |      |       |       |       |                   |

| Contrast Ratio  | <ul> <li>White Raster</li></ul> |      | 100:1 | 150:1 |       | -                 |

|                 |                                 |      |       |       |       |                   |

|                 | of the center of the panel.     |      |       |       |       |                   |

| xy Chromaticity | White Raster Image              | х    | 0.303 | 0.313 | 0.323 | -                 |

|                 | Measure the chromaticity        |      |       |       |       |                   |

|                 | of the center of the panel.     | у    | 0.319 | 0.329 | 0.339 | -                 |

|                 |                                 |      |       |       |       |                   |

Note : Measurement conditions of the optical characteristics are as follows.

# [Measurement Conditions]

| Supply Voltage                                                         |                                                                                         | =3.30V, VIO_serial=3.3       |             |                    |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------|-------------|--------------------|

| Video Signal Input                                                     | DAVCC=3.30V<br>: YCbCr 16bit<br>White Y=FFh, Cb=                                        | 80h, Cr=80h                  | CS-10       | a Minolta Made     |

| Gamma Correction<br>LED brightness register                            | : 2.1<br>: Setting at maximum                                                           | (Focal plane indicat         | ion )       |                    |

| Temperature<br>Luminance & Color Mete<br>xy Chromaticity<br>Brightness | : Room Temp. (25°C<br>: CS-100A manufactu<br>: Measured on white<br>: Measured on white | ured by Konica minolta image | 204mm       |                    |

|                                                                        |                                                                                         |                              | •           | Diameter : φ1.3    |

|                                                                        |                                                                                         |                              | (Center are | ea of display)     |

|                                                                        |                                                                                         |                              | Fig.12. Op  | otical Measurement |

|                                                                        |                                                                                         |                              |             |                    |

|                                                                        |                                                                                         |                              |             |                    |

# 6.2 Lens Optical Characteristics (Design value)

## **Table15. Lens Optical Characteristics**

| Parameter                             | Standard value                                                                                                                | Unit  | Remarks                                              |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------|--|

| Magnification of ocular               | 18.4                                                                                                                          | times | (250/f)                                              |  |

| Focal length                          | 13.59                                                                                                                         | mm    |                                                      |  |

| Diameter of exit pupil                | φ5.0                                                                                                                          | mm    |                                                      |  |

| Eye Point                             | 12.5                                                                                                                          | mm    | From the eye side lens top to the viewpoint.(0d)     |  |

| Adjustment range of the diopter       | -3 ~ +1                                                                                                                       | D     |                                                      |  |

| Wavelength range                      | 440~650                                                                                                                       | nm    |                                                      |  |

| Lens constitution                     | 3                                                                                                                             | pcs   |                                                      |  |

| MTF<br>(Modulation transfer function) | Center : 94.1% / 40lp/mm<br>V (Y=1.485): M 71% / 40lp/mm<br>S 67% / 40lp/mm<br>H (Y=1.98): M 62% / 40lp/mm<br>S 39% / 40lp/mm |       |                                                      |  |

| Peripheral brightness                 | 91.9                                                                                                                          | %     |                                                      |  |

| DISTORTION                            | -0.54                                                                                                                         | %     | Optics Distortion (Diagonal)                         |  |

|                                       | -0.13                                                                                                                         | %     | TV Distortion                                        |  |

| Chromatic aberration of magnification | 0.0057                                                                                                                        | mm    | Diagonal, the distance between<br>C line and g line. |  |

|                                       | 0.0038                                                                                                                        | mm    | Diagonal, the distance between d line and F line.    |  |

| Coating                               | No Coating                                                                                                                    |       |                                                      |  |

\*1 : All values are at room temperature, under the general environment.

\*2 : All values are theoretically calculated by CFM.

## **6.3 Visual Specifications**

## Conditions of inspection

At room temperature and normal humidity, inspect the display by microscope of 20 magnification focusing on the display focal plane.

Dither mode setting : 1/2bit spatial dither & 1/4bit temporal dither Gamma correction setting : 2.1 Color space/ Color offset register setting : 0h(All setting)

Input Signal Level 0%: (Y,Cb,Cr)=(0h,80h,80h), 100%: (Y,Cb,Cr)=(FFh,80h,80h)

| Table 16-1 | . Display | area | visual | defects |

|------------|-----------|------|--------|---------|

|------------|-----------|------|--------|---------|

| Subject Area    | Item          | Size(Average) Allowable Quantity[Unit:pcs]    |                   |                  |  |  |

|-----------------|---------------|-----------------------------------------------|-------------------|------------------|--|--|

|                 |               | [Unit : µm²]                                  | Bright/White spot | Dark/Black point |  |  |

|                 |               |                                               | Scratch(White)    | Scratch(Black)   |  |  |

| Display area    | Line Out      | 1 pixel line(line/column                      | 0                 | 0                |  |  |

| Dummy area      |               |                                               |                   |                  |  |  |

| Aperture mask   | Large Spot    | S > 121                                       | 0                 | 0                |  |  |

|                 |               |                                               |                   |                  |  |  |

|                 | Medium Spot   | 121 <u>&gt;</u> S > 61                        | 3                 | 3                |  |  |

|                 |               |                                               |                   |                  |  |  |

|                 | Small Spot    | 61 <u>&gt;</u> S                              | No clumping       |                  |  |  |

|                 |               |                                               |                   |                  |  |  |

| Display area    | Texture       | According to limit same                       | ple               |                  |  |  |

|                 |               |                                               |                   |                  |  |  |

| PBS Upper side/ | Contamination | None when focusing on the display focal plane |                   |                  |  |  |

| Lower side      | Scratch       |                                               |                   |                  |  |  |

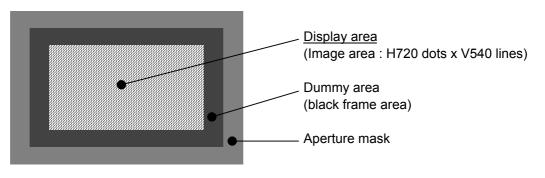

Note 1) Definition of display area is shown in Figure 13.

Note 2) Contaminations and scratches with line shape are judged after converting the size into area.

Fig. 13. Display area

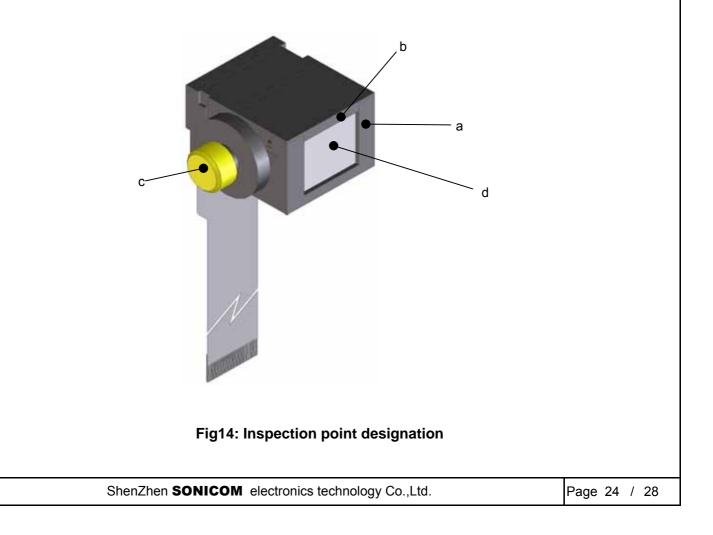

# [Appearance and Mechanical feature]

| Item<br>(a-d: Refer to Fig.14 | 4)                                | Spec.                                                     | Measuring condition / Note       |

|-------------------------------|-----------------------------------|-----------------------------------------------------------|----------------------------------|

| a<br>b<br>c                   | Scratch<br>Burr<br>Contamination  | Should not degrade appearance quality. (*1)               | With naked eyes.                 |

| d                             | Contamination<br>Scratch<br>Trash | Should not degrade appearance quality. (*1)               | *2                               |

| Lens                          | Contamination<br>Scratch<br>Trash | Should not degrade appearance quality. (*1)               | *2                               |

|                               | Blur                              | Should not degrade appearance quality. (*1)               | Focusing on the displayed image. |

| Dial movement                 | Rotary torque                     | TBD to TBD cNm                                            |                                  |

|                               | Operational feeling               | Should move smoothly.<br>No excess backlash and rattling. |                                  |

- \*1 : Limit samples are to apply to the criteria for judgement, if necessary.

- \*2 : Focusing on the displayed image. Additionally inspect with a white image keeping an eye away from the eyepiece lens.

#### 7.Serial Number

```

1) Serial No

<u>X</u>

\underline{X} \underline{X} \underline{X} \underline{XXXXXX}

a b

d

С

a : Manufacturing Year -- Last digit of the western calendar year

b : Manufacturing Month -- shown by 1 digit as below

Jan. ... A

Jul. ... G

Feb. ... B

Aug. ... H

Mar. ... C

Sep. ... I

Apr. ... D

Oct. ... J

May ... E

Nov. ... K

Jun. ... F

Dec. ... L

c : Serial No. (Maximum 6 digits)

d : Model Identification

FLxxxx ... TBD

2) Label Color

TBD

3) Labeling Position : Refer to the following figure.

Labeling Position

```

## 9. Reliability

## 9.1 Reliability Test

| Item                         | Test Condition                             | Spec.                                  |

|------------------------------|--------------------------------------------|----------------------------------------|

| High Temperature             | Ta=83°C 240hrs                             | Judgement is performed after           |

| Storage Test                 | * Ta : Ambient temperature of this product | an hour storage at room temp.          |

| Low Temperature              | Ta= -30°C 240hrs                           |                                        |

| Storage Test                 |                                            | Should not have any mechanical and     |

| High Temperature             | Ta=60°C RH=90% 240hrs                      | electrical malfunction of product that |

| High Humidity Storage Test   |                                            | affects normal product operation.      |

| High Temperature             | Tp=70°C 240hrs                             |                                        |

| Operating Test               | * Tp: Surface temperature of panel glass   |                                        |

| Low Temperature              | Ta= - 10°C 240hrs                          |                                        |

| Operating Test               |                                            |                                        |

| High Temperature             | Ta=40°C RH=90% 240H                        |                                        |

| High Humidity Operating Test |                                            |                                        |

| Heat Shock Cycle Test        | -30 ~ 80°C 30min/30min                     |                                        |

|                              | 30 cycles                                  |                                        |

|                              |                                            |                                        |

\* Ta : Ambient temperature of the product

## 9.2 Electrostatic Discharge Test

| Item                         | Test Condition                          | Spec.                                  |

|------------------------------|-----------------------------------------|----------------------------------------|

| Electrostatic discharge test | C=200PF R=0Ω V=+/-200V                  | Should not have any mechanical and     |

| Mechine Model                | Discharge between Power supply terminal | electrical malfunction of product that |

|                              | and each signal pin 3 times each.       | affects normal product operation.      |

Note : The above tests are performed at room temperature and normal environment.

#### 9.3 Mechanical Reliability Test

| Item           | Test Condition                                                                                                              | Spec.                                                                                                       |

|----------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Vibration Test | Vibration amplitude : 1.5mm<br>Frequency : 10-55Hz<br>Duration time : each axis 30min(X, Y, Z)                              | Should not have any mechanical and electrical malfunction of product that affects normal product operation. |

| Drop Test      | Height : 20cm<br>Drop time : each axis 3 times(X, Y, Z)<br>Let products drop to a hard wooden<br>board or a concrete floor. |                                                                                                             |

Note : The above tests are performed at room temperature and normal environment.

## 9.4 Shipping Package Test

| Item                        | Test Condition                                                                                                                                                     | Spec.                                                                                                       |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Vibration Test( in package) | Frequency : 10-50-10Hz                                                                                                                                             | Should not have any mechanical and electrical malfunction of product that affects normal product operation. |

| Drop Test( in package)      | Drop Height : 75cm<br>1corner 3 edges 6 planes<br>Drop time : each axis 1 time(3edges/6planes)<br>Let products drop to a hard wooden<br>board or a concrete floor. |                                                                                                             |

Note : The above tests are performed at room temperature and normal environment.

#### **10. Special Handling Criteria**

- \* To prevent dust and particulate contamination, It is recommended to open the seal on these trays in a Class 10,000(or better) or equivalent room for incoming inspection or manufacturing integration.

- \* Do not stack trays higher than **TBD**, or place other heavy material on the trays to prevent damage to the sensitive optical components on the display.

- \* Do not touch the surface of the polarizing film with bare fingers. When removing particulate contaminations on the film, wipe carefully the particulate contaminations off the film with alcohol-soaked soft cloth or cotton swab without any damage to the film.

- \* Do not use air blow to remove particulate contaminations. In case of strong air blow cleaning very close to the product, particles may intrude into the product.

- \* During either integration or storage, do not allow any moisture or solvent to contact the polarizing film and do not allow condensation to form on the product.

- \* When handling the product, please pay attention to keep the product static-free and non-chargeable, especially, do not touch the conductive work surface of the product.

#### 11. Environmental Standards

\* The product is compliant with RoHS Directive[EUROPEAN DIRECTIVES 2002/95/EC on the restriction of the use of certain hazardous substances in electrical and electoronic equipment].

#### 12.Others

When the issue that is not described in this document arises, the both parties will mutually solve it.